Many vendors have moved to Si2’s OpenAccess platform, but a range of tools are based on other formats. Some of these tools are supported by larger companies, including Analog Devices’ LTSpice, Google/Skywater’s XSCHEM and SLED from Dolphin Design.

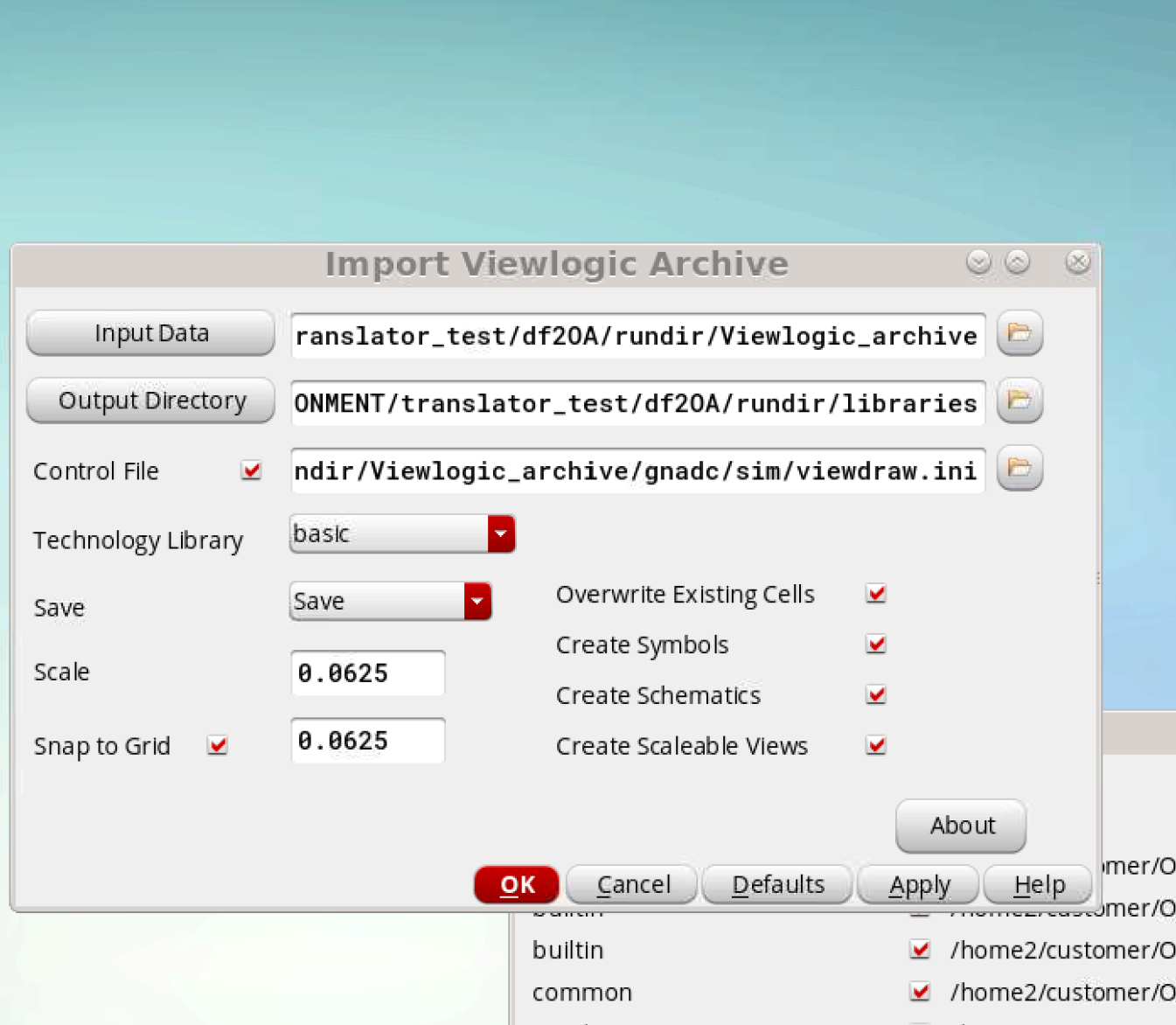

In addition, many circuits have been created and archived using older tools such as Viewlogic, where licenses may not even be available to open the circuits for editing or review.

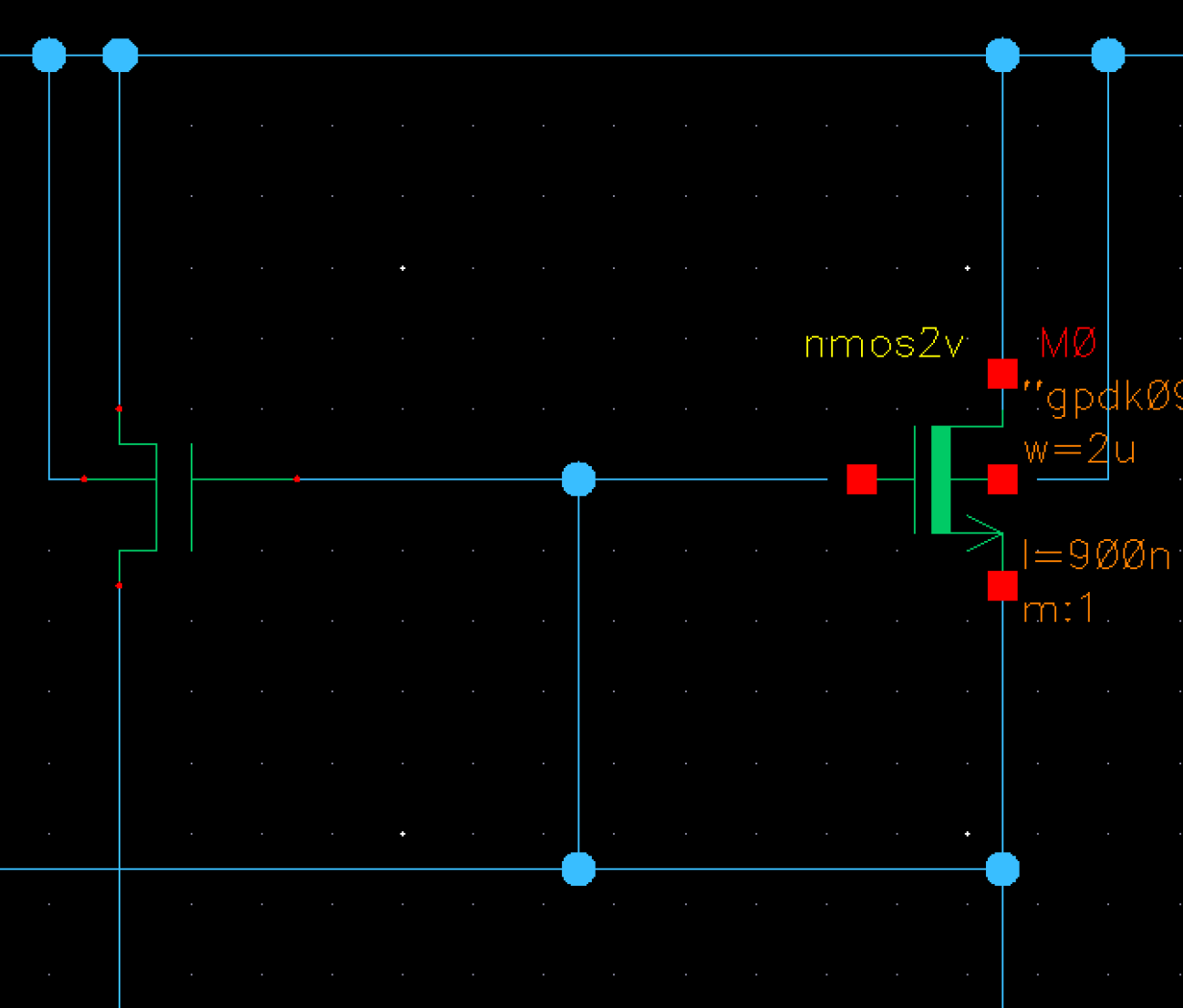

IN2FAB’s circuit migration service group sees databases from a wide variety of sources, including proprietary and external tools. This has led to the development of direct database-level translators which import external data directly to Cadence Virtuoso. Single and multiple libraries are translated along with PDK level components to reconstruct an entire circuit hierarchy in a single pass. Symbol and schematic design directories and files are read directly and output in Cadence Virtuoso format.