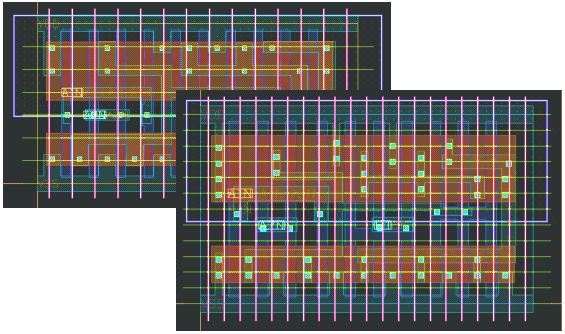

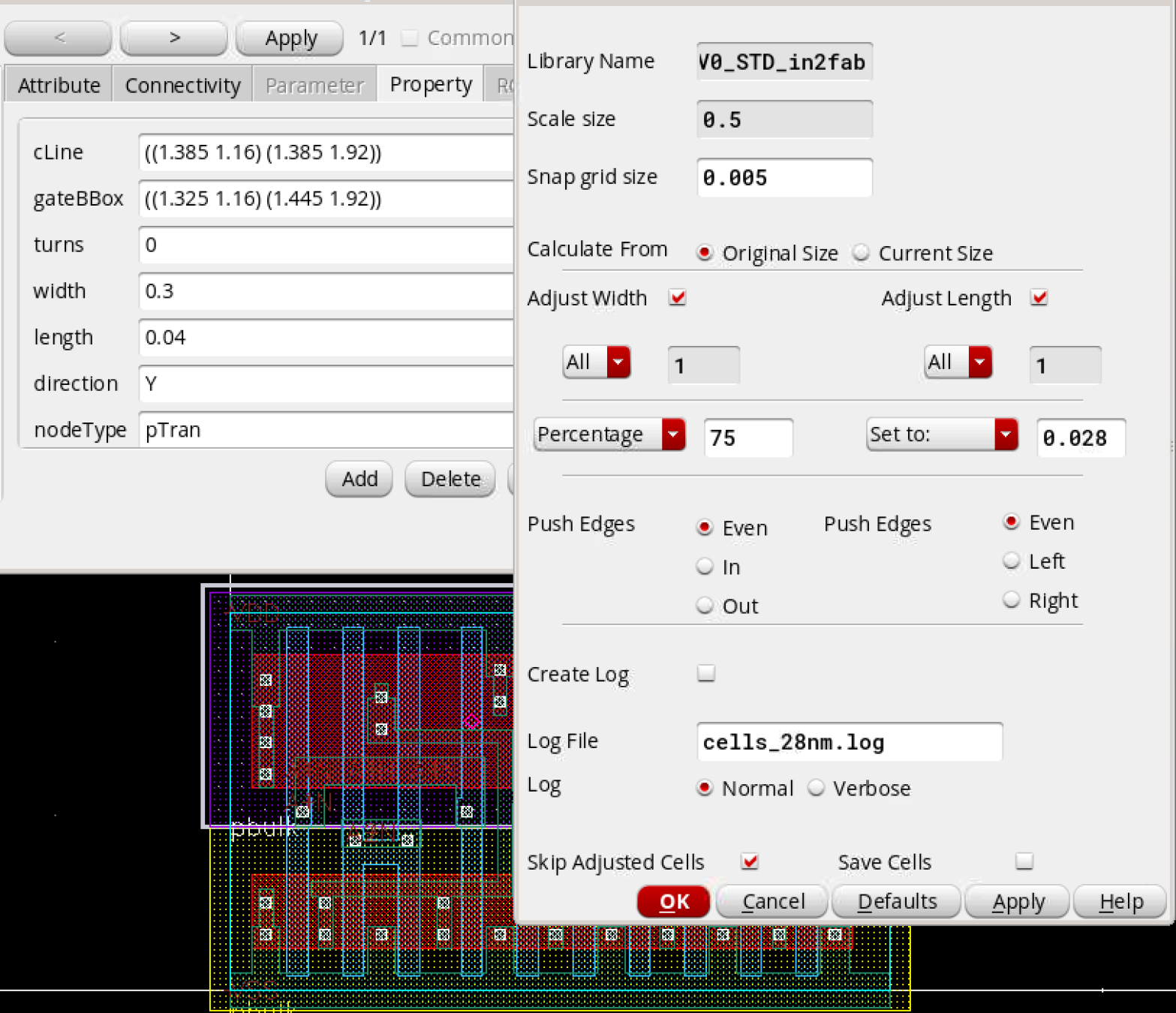

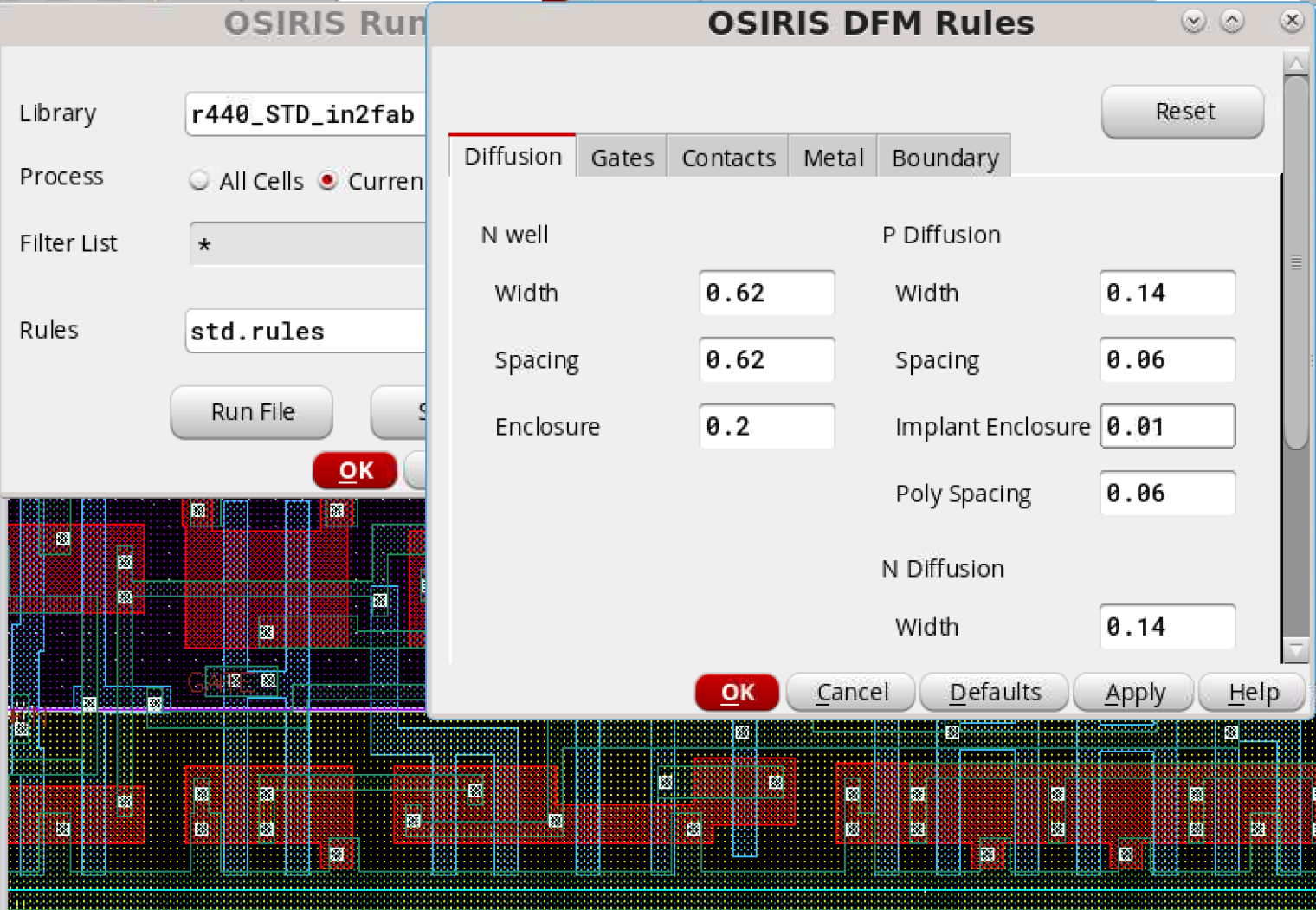

Unlike analog layout based on parameterized cells, standard cells are usually constructed of polygons that make up the devices and interconnect. By identifying the elements of the layout that make up the transistors, the standard cell migration technology can update gate dimensions, then adjust the rest of the layout to meet design rules.

IN2FAB's standard cell migration technology can process hundreds of cells in a matter of minutes, to move them to a new technology or simply apply new rules. Schematics for each cell are updated to contain new symbols and parameters, while the layout is converted to match the new manufacturing process requirements and rules.

By adopting this approach, cell libraries maintain their structure and device positioning, while the shapes for each device are adjusted to match new design rules.