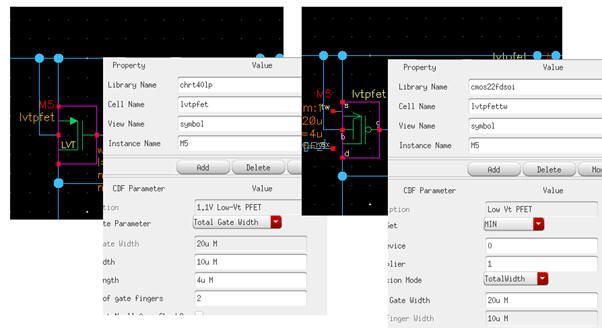

Schematic and layout data are translated through map files that describe the old and new circuit elements along with pin and parameter information. Core circuit components will be replaced with equivalent devices from the new PDK and any standard cells placed in the analog hierarchy should also be swapped to elements from a library in the new process.

Physical information including symbols, wires and pins are migrated and adapted to suit the new PDK, with automatic position adjustment, rewiring, short location and connectivity checking tools. Some SOI transistors have extra pins for body biasing so these can be connected as required. Automatic short location within the migration tools picks up any places where a new pin shorts to an existing wire and re-routes to fix the problem.

Parameter limits play an important part in process migration and tools must recognise instances that must change in the target process due to limits in maximum or minimum values and adapt them accordingly. Similar changes are often required in passive components where new sizes or number of segments are required. OSIRIS migration tools calculate the values automatically so there is no need for engineers to calculate conversion factors.

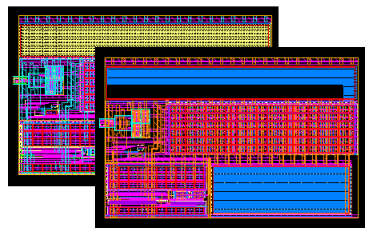

Once the schematic migration is complete and the test benches are converted, the circuit can run through first level simulation. This should confirm overall functionality of the system in the new process as the simulation is using models from the 22FDX® libraries.

A migrated schematic means that designers can get to the circuit tuning level without having to worry about building an entirely new design from scratch. Once this migration flow is configured, even large designs can be migrated and ready for simulation in a matter of hours.